Микропроцессоры компании Analog Devices образуют два семейства: ADSP21xx и ADSP21xxx.

Семейство ADSP21xx - набор однокристальных 16-разрядных микропроцессоров с общей базовой архитектурой, оптимизированной для выполнения алгоритмов цифровой обработки сигналов и других приложений, требующих высокопроизводительных вычислений с фиксированной точкой. Микропроцессоры этого семейства на сегодняшний день насчитывают 15 представителей, которые отличаются друг от друга, в основном, расположенными на кристалле периферийными устройствами, такими как кэшпамять, таймеры, порты и т. п.

Второе семейство микропроцессоров ADSP210xx объединяет 32-разрядные микропроцессоры, ориентированные на сигнальные алгоритмы, требующие выполнения вычислений с плавающей точкой. Семейство представлено микропроцессорами ADSP21010, ADSP21020, ADSP21060, ADSP21062, ADSP21160, ADSP-TS001.

В рамках каждого семейства микропроцессоров обеспечивается совместимость снизу вверх по системе команд. Старшие представители семейства обладают большей производительностью и содержат на кристалле дополнительные функциональные блоки.

В дальнейшем изложении при рассмотрении сигнальных микропроцессоров компании Analog Devices будем выделять общие архитектурные и конструктивные особенности каждого семейства, отмечая наиболее существенные отличия отдельных его представителей.

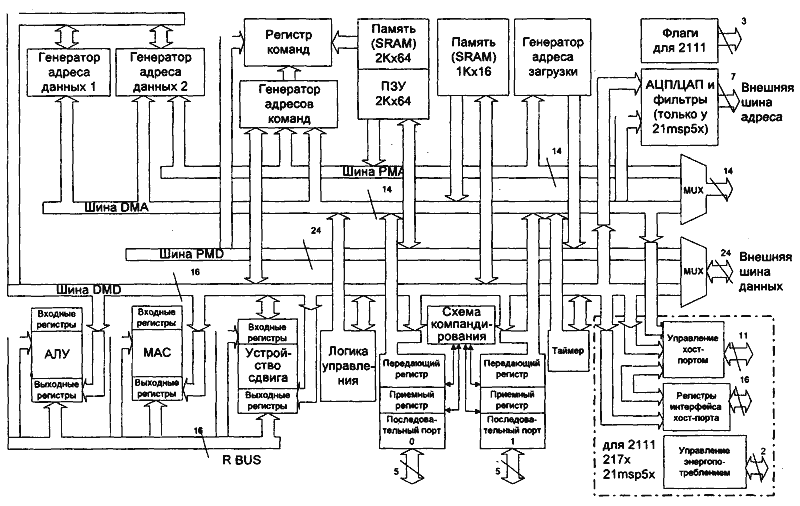

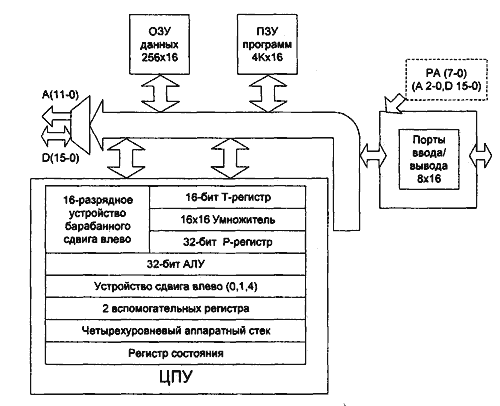

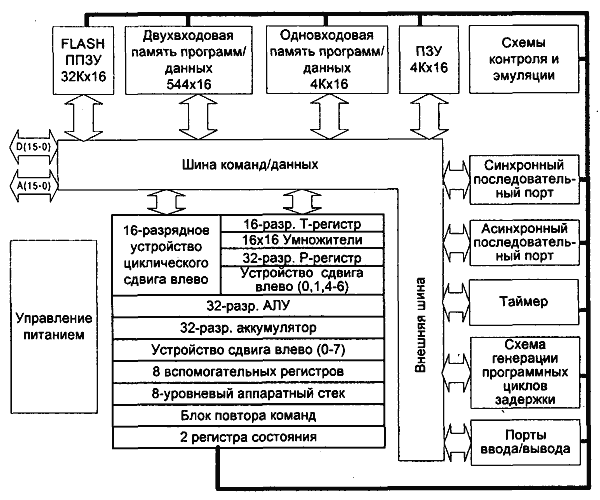

Микропроцессоры семейства ADSP21xx успешно конкурируют с аналогичной продукцией компаний Motorola и Texas Instruments благодаря высокой производительности и низкой цене, а также наличию развитых аппаратных и программных средств разработки прикладных систем. Высокая производительность процессоров на сигнальных алгоритмах достигается за счет многофункциональной и гибкой системы команд, аппаратной реализации большинства типичных для сигнальной обработки операций, высокой степени параллелизма процессов в микропроцессоре, сокращения командного цикла. Микропроцессоры ADSP21xx имеют модифицированную гарвардскую архитектуру, в рамках которой предусматривается возможность доступа в память команд при ее физическом разделении с памятью данных. Аналогичную архитектуру, ставшую для процессоров ЦОС стандартом де-факто, имеют многие другие процессоры, в том числе и TMS320xxx. Обобщенная структура микропроцессора ADSP21xx приведена на рис. 1.

Рис. 1. Обобщенная структура микропроцессора ADSP21xx

Каждый микропроцессор семейства содержит три независимых функциональных блока: АЛУ, умножитель с накоплением (MAC) и устройство барабанного сдвига. Каждый блок непосредственно оперирует с 16-разрядными данными и обеспечивает аппаратную поддержку вычислений с различной точностью.

Микропроцессор содержит генератор адресов команд и два генератора адресов данных, обеспечивающие адресацию к данным и командам, расположенным как во внутренней, так и во внешней памяти. Параллельное функционирование генераторов сокращает длительность выполнения команды, позволяя за один такт выбирать из памяти команду и два операнда.

Последовательные порты обеспечивают интерфейс с большинством стандартных последовательных устройств, а также с аппаратными средствами сжатия/восстановления данных, использующими А- и µ-законы компандирования.

Порт интерфейса с хост-процессором позволяет без дополнительных интерфейсных схем взаимодействовать с хост-процессором системы, в качестве которого может использоваться как процессор данного семейства, так и другой микропроцессор.

Микропроцессор ADSP-21msp5x отличается наличием аналогового интерфейса, позволяющего вводить и выводить обрабатываемый сигнал в аналоговой форме. В состав интерфейсных блоков входят АЦП, ЦАП, цифровой и аналоговый фильтры, параллельный интерфейс.

Микропроцессор ADSP-2181 содержит внутренний порт ПДП и байтовый порт ПДП, которые обеспечивают быстрый обмен с внутренней памятью. Внутренний порт ПДП поддерживает асинхронный обмен с памятью программ, а байтовый порт позволяет записывать и читать как команды, так и данные.

Микропроцессоры компании Analog Devices отличает высокая степень параллелизма внутренних операций. За один такт процессор может:

Микропроцессор, имеющий соответствующее устройство, может в этом же такте:

Основные характеристики микропроцессоров семейства ADSP-21xx приведены в табл. 1

Таблица 1. Основные характеристики микропроцессоров семейства 21хх

|

Возможности |

2101 |

2103 |

2105 |

2115 |

2111 |

2171 |

2173 |

2181 |

2183 |

21msp58 |

|

АЛУ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Блок MAC |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Сдвиг |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Генератор адресов данных |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Генератор адресов команд |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

ОЗУ данных, Кслов |

1 |

1 |

0,5 |

0,5 |

1 |

2 |

2 |

16 |

16 |

2 |

|

ОЗУ команд, Кслов |

2 |

2 |

1 |

1 |

2 |

2 |

2 |

16 |

16 |

2 |

|

Таймер |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Многоканальный последовательный порт |

+ |

+ |

- |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Последовательный порт |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

|

Порт хост-интерфейса |

- |

- |

- |

- |

+ |

+ |

+ |

- |

- |

+ |

|

Порт ПДП |

- |

- |

- |

- |

- |

- |

- |

+ |

+ |

- |

|

Аналоговый интерфейс |

- |

- |

- |

- |

- |

- |

- |

- |

- |

+ |

|

Напряжение питания, В |

5 |

3,3 |

5 |

5 |

5 |

5 |

3,3 |

5 |

3,3 |

5 |

|

Производительность (MIPS) |

20 |

10 |

13.8 |

20 |

20 |

33 |

20 |

33 |

33 |

26 |

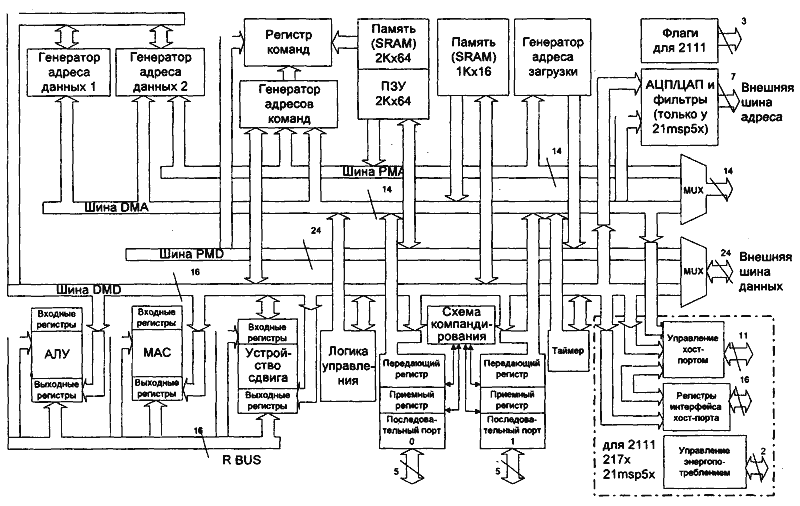

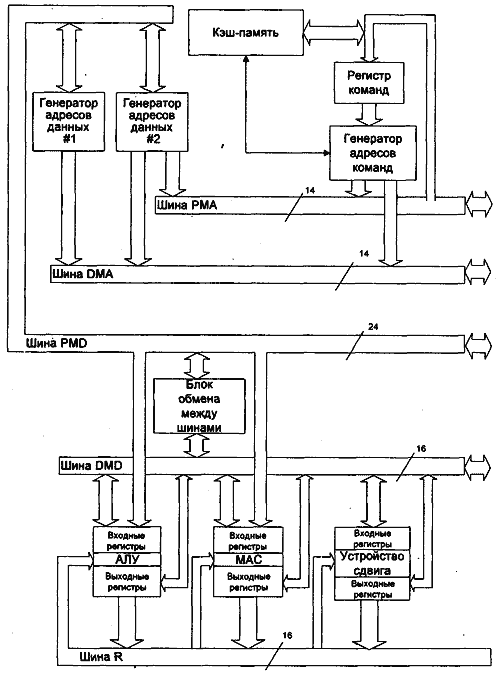

Общее для семейства ADSP-21xx микропроцессорное ядро изображено на рис. 2. Арифметико-логическое устройство микропроцессора выполняет стандартный набор арифметических и логических операций, включая деление. Устройство MAC выполняет операции умножения со сложением (вычитанием) за один такт. Устройство сдвига осуществляет арифметические и логические сдвиги операндов, нормализацию и возведение в степень. Функциональные устройства микропроцессора могут обмениваться результатами выполнения операций по шине внутренних результатов.

Рис. 2. Структура микропроцессорного ядра ADSP21xx

Внутренние функциональные блоки связаны между собой с помощью пяти шин: шина адресов памяти данных (DMA), шина адресов памяти команд (РМА), шина данных памяти данных (DMD), шина данных памяти команд (PMD) шина внутренних результатов (R). Первые четыре шины имеют мультиплексированный внешний интерфейс в виде шины адреса и шины данных (см. рис. 2).

По системе команд все микропроцессоры совместимы снизу вверх. Отдельные представители семейства- ADSP-2171, 2181, 21msp5x - имеют дополнительные и расширенные команды.. Каждая команда выполняется за один такт. Многофункциональные команды микропроцессора объединяют несколько пересылок данных с арифметико-логической обработкой.

Все устройства микропроцессора - 16-разрядные и оперируют с данными в формате с фиксированной точкой. Числа представляются либо как беззнаковые, либо в дополнительном коде. Логические операции выполняются над битовыми строками.

Совершенствование данного семейства микропроцессоров идет в направлении повышения тактовой частоты, снижения энергопотребления и расширения коммуникационных возможностей процессора.

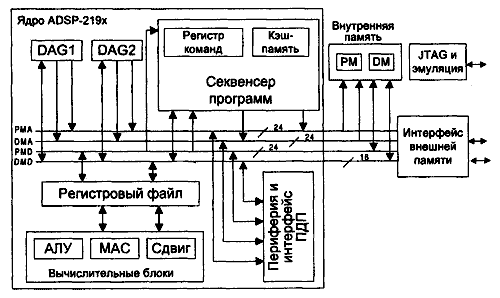

Новый микропроцессор семейства ADSP-219x содержит модифицированное ядро, которое рассматривается компанией Analog Devices как ключевой элемент в технологии создания перспективных 16-разрядных сигнальных процессоров общего назначения и процессоров для встроенных решений.

Специальные схемотехнические решения на основе данного ядра и программное обеспечение планируется создавать непосредственно для заказчика, под конкретно заданные требования и характеристики. Для приложений, требующих высокой производительности, будут создаваться процессоры, содержащие несколько ядер на одном кристалле. В будущем предполагается выпуск микропроцессоров, содержащих 4 ядра на одном кристалле и обладающих производительностью 1,2 миллиарда MAC в секунду на 1 квадратный дюйм площади кристалла.

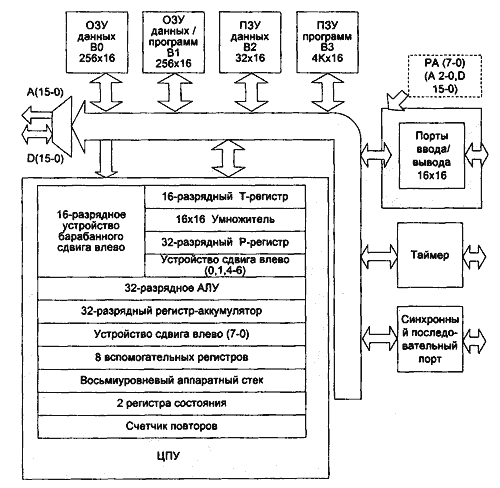

Структура микропроцессора ADSP-219x показана на рис. 3.

Рис. 3. Структура микропроцессора ADSP-219X

По сравнению с процессорами семейства ADSP-218x, имеющими 14-разрядную шину адреса, в семействе ADSP-219x используется 24-разрядная шина адреса, что позволяет осуществлять прямую адресацию в пределах 64 Кслов или страничную адресацию в пределах 16 Мслов. Адресный генератор процессоров семейства 219х поддерживает все ранее использованные и пять новых режимов адресации.

ADSP-219x программно совместим с предыдущими микропроцессорами семейства ADSP-21xx, обладает большей производительностью (до 300 MIPS) и меньшим энергопотреблением (0,4 мBт/MIPS).

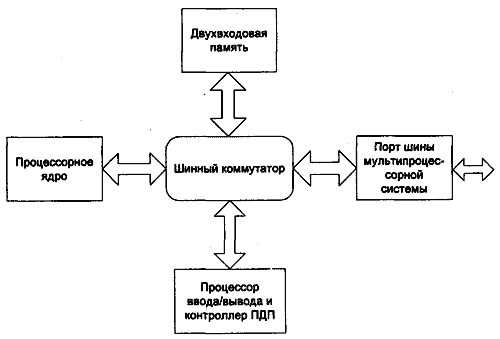

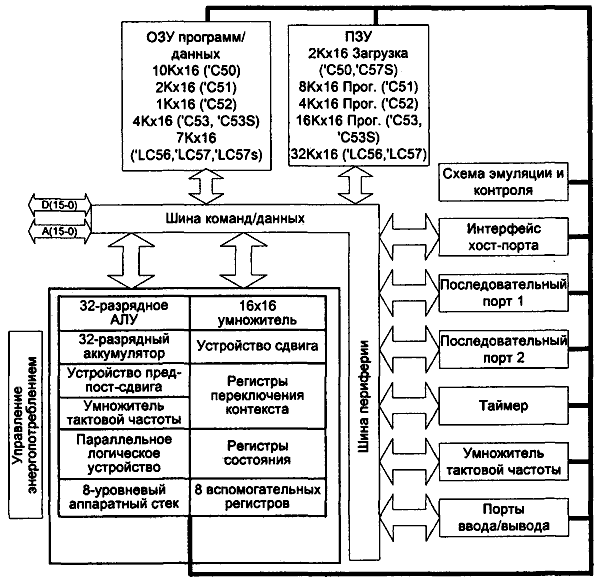

Следующее поколение семейства ADSP 21ххх представлено микропроцессорами ADSP-21060 и ADSP-21062. Будучи сходными с ранее рассмотренными микропроцессорами ADSP-210xx по структуре ядра и совместимыми снизу-вверх по системе команд, эти микропроцессоры обладают существенными архитектурными отличиями, что позволило разработчикам выделить их в отдельное архитектурное семейство SHARC (Super Harvad Architecture Computer). Архитектура SHARC (рис. 5) продолжает развитие транспьютерного направления в микропроцессорной технике и задает новый стандарт интеграции сигнальных процессоров в мультипроцессорную систему. Эта архитектура является примером гармоничного сочетания принципов по строения распределенных и связанных систем, объединяя в себе простоту и эффективность масштабирования распределенных систем с удобством программирования систем с разделяемой памятью.

Рис. 6. Архитектура SHARC

В SHARC-микропроцессоре объединены высокоэффективное процессорное ядро, выполняющее обработку данных в формате с плавающей точкой, интерфейс с хост-процессором, контроллер ПДП, последовательные порты, коммуникационные линки и разделяемая шина.

На тактовой частоте 40 МГц производительность микропроцессоров составляет 80 MIPS и 120 Mflops.

Шинный коммутатор соединяет ядро процессора с независимым процессором ввода/вывода, двухвходовой памятью и портом шины мультипроцессорной системы. Вычислительные модули на базе микропроцессоров ADSP-2106x выпуска ются в виде микропроцессорных кластеров: платы с шинным интерфейсом ISA, PCI или VME содержат от 3 до 8 узлов. Производятся также мезонинные модули SHARCPAC и TRANSPAC, устанавливаемые в специальныеразъемы материнских плат.

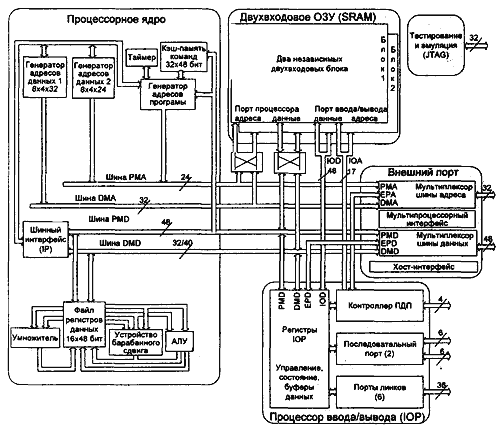

Вычислительные модули на базе микропроцессоров SHARC используются в системах радио- и гидролокации, в системах распознавания речи и обработки изображений, в средствах телекоммуникации и медицинской диагностики. Структура микропроцессора ADSP-2106x приведена на рис. 7.

Рис. 7. Структура микропроцессора ADSP-2106X

Микропроцессоры ADSP-21060 содержат на кристалле 4 Мбит статической двухвходовой памяти, которая может быть сконфигурирована для работы 16-битными (256 Кслов), 32-битными (128 Кслов) и/или 48-битными (80 Кслов) словами. Вся память может быть произвольно разделена на память программ и память данных.

Другой представитель этого семейства - микропроцессор ADSP-21062 - отличается от ADSP-21060 меньшим объемом внутрикристальной памяти (2 Мбит).

Общее адресуемое пространство микропроцессора составляет 4 Гслова. Встроенный контроллер внешней оперативной памяти позволяет задавать различное число генерируемых тактов ожидания и поддерживает странич-ный обмен с динамической памятью.

Интерфейс с хост-процессором обеспечивает простое соединение со стандартной 16- или 32-разрядной микропроцессорной шиной. Передача данных через интерфейс осуществляется асинхронно, со скоростью, ограниченной тактовой частотой микропроцессора. Хост-интерфейс доступен через внешний порт и отображается в адресное пространство микропроцессора. Четыре канала контроллера ПДП обеспечивают обмен данными и командами через хост-интерфейс с минимальным участием процессорного ядра. Расположенный на кристалле 10-канальный контроллер ПДП обеспечивает обмен данными между внутренней и внешней памятью, периферийными устройствами, хост-процессором, последовательными портами и линками микропроцессора.

ADSP-21060 имеет два синхронных последовательных порта для связи с разнообразными периферийными устройствами. Максимальная скорость передачи данных через последовательный порт составляет 40 Мбит/с. Передача может осуществляться одновременно в двух направлениях в режиме ПДП. В процессе обмена может выполняться дополнительное преобразование данных, такое, например, как мю- или А-компандирование. ADSP-21060 предоставляет разработчикам широкие возможности по созданию мультипроцессорных сигнальных систем. Общее адресное пространство может быть разделено между несколькими процессорами. Обеспечивается автоматическая поддержка семафоров для последовательностей операций чтение-изменение-запись в память. Встроенная распределенная шинная логика позволяет создавать системы, содержащие до 6 взаимодействующих процессоров ADSP-21060 и хост-процессор. Межпроцессорное управление осуществляется с помощью механизма векторов прерывания. Дополнительные возможности ввода/вывода процессору предоставляют шесть 4-разрядных линков. Линки передают данные по переднему и заднему фронту тактового импульса, обеспечивая, таким образом, передачу 8 бит за такт. Линки используются в мультипроцессорных системах для соединений типа "точка-точка". Передача данных по линку может осуществляться 32-или 48-разрядными словами непосредственно в процессорное ядро или, с использованием ПДП-канала, во внутреннюю память. Каждый линк содержит собственные буферные входные и выходные регистры. Максимальная скорость межпроцессорного обмена через все линки или внешний порт составляет 240 Мбайт/с. Загрузка микропроцессора может осуществляться из ПЗУ, хост-процессора или по одному из линков.

Линки микропроцессора

Каждый линк Lx, х = {0, 1, ..., 5}, состоит из 4 двунаправленных линий данных LxDAT (0, 1, 2, 3), а также из двух двунаправленных управляющих линий LxCLK и LxACK, обеспечивающих асинхронную передачу в режиме "запрос-ответ".

Порты на противоположных концах линка настраиваются на передачу и прием, либо находятся в третьем состоянии.

Порт каждого линка может выбрать для передачи или приема один из 6 буферов. Данные читаются из буферов и пишутся в буферы под управлением контроллера прямого доступа в память (ПДП) или процессора (ЦПУ). Буферы линков 5, 4, 3, 2, 1, 0 поддерживаются каналами ПДП 7, 6, 5, 4, 3, 1 соответственно.

Контроллер ПДП программируется для работы с буфером путем задания размера буфера, начального адреса в памяти, приращения адреса, а также направления передачи. Когда контроллер ПДП завершает операцию, вырабатывается прерывание, индивидуальное для каждого из 10 ПДП-каналов.

Буферы могут быть читаемы или пополняемы процессором посредством операций чтения/записи в области памяти внешних устройств. Если предпринимается попытка чтения из пустого буфера, процессор должен перейти в ждущее состояние до тех пор, пока не поступят данные извне. Естественно, при записи в заполненные буферы операция также должна быть приостановлена, вплоть до появления свободного места в буфере.

В приложениях, в которых задержка, вносимая контроллером ПДП, неприемлемо велика, процессор может непосредственно работать с буферами. Контроллер ПДП должен быть переведен в неактивное состояние.

При работе линков вырабатываются следующие прерывания:

Асинхронный "запрос-ответ"

Передающий ADSP 2106х выставляет высокий уровень на LxCLK при выдаче очередного полубайта на линии LxDAT. Изменение этого уровня используется принимающим ADSP-2106x для приема полубайта. Принимающий ADSP-2106x выставляет LxACK, когда принято очередное слово в буфер. Передающий ADSP-2106x анализирует LxACK в начале передачи каждого слова. Если требуемый уровень LxACK в этот момент отсутствует, то передача слова не начинается.

Передающий ADSP-2106x оставляет LxCLK высоким, если LxACK отсутствует. При появлении LxACK, LxCLK становится низким и начинается передача следующего слова.

Принимающий буфер может заполняться, если выполняются высокоприоритетная ПДП- или цепочечная операция, при этом LxACK не выставляется. Однако сразу после завершения ПДП выставляется LxACK. Данные "защелкиваются" в принимающем буфере по спадающему уровню LxCLK. Передача полубайта данных происходит каждый такт ADSP-2106x или дважды за такт, если установлен специальный бит LCKx2.

Буферы

Каждый буфер состоит из внешнего и внутреннего регистров. При передаче внутренний регистр используется для приема данных из внутренней памяти под управлением ПДП-контроллера или ЦП. Внешний регистр используется для распаковки полубайтов для порта линка (старший полубайт следует первым). Эти два регистра формируют FIFO-очередь. Два слова могут быть помещены в буфер прежде, чем вырабатывается сигнал "заполнено". Если регистр пуст, уровень сигнала LxCLK становится низким.

При приеме внешний регистр упаковывает принимаемые полубайты в слова и передает их через внутренний регистр в память под управлением ПДП-контроллера или ЦП. Если ПДП-контроллер или ЦП не успели извлечь данные из внутреннего регистра и оба регистра буфера заняты, сигнал LxACK не выдается, и прием прекращается.

Длина регистров настраивается программно и составляет 32 или 48 битн. Для работы с 40-битными данными или командами должна устанавливаться длина регистров 48 битн.

Установление соглашения по использованию линка

Прежде чем два процессора начинают взаимодействовать по связывающему их линку, должно быть определено: кто из процессоров будет передавать данные, а кто принимать. Для этого используется обмен маркером. При начальной установке маркер (программно доступный флаг) устанавливается в одном из процессоров, определяя его как "хозяина" (master) линка и разрешая ему передачу.

Если принимающий порт желает стать "хозяином" линка для передачи данных, он должен выставить сигнал на LxACK (запрос данных) для текущего "хозяина" линка. "Хозяин", используя программный протокол, определяет, когда приходит подтверждение данных, а когда запрос на получение маркера.

Если "хозяин" решил передать маркер, он посылает обратно определенный пользователем в качестве маркера идентификатор и сбрасывает собственный маркер. Одновременно ведомый процессор проверяет полученные данные и, если в них содержится необходимое слово, то он устанавливает свою метку, переходя в состояние ведущего процессора.

Если полученные данные не содержат необходимого идентификатора, то ведомый процессор должен понять, что ведущий начинает новую передачу данных.

Ведущий процессор может также запросить получение данных с помощью программного протокола путем посылки маркера без получения запроса по LxACK.

Контроллер ПДП и порты линков передают данные между собой с помощью того же самого протокола ("запрос-подтверждение"), который используется всеми портами ввода/вывода.

Интерфейс с хост-компьютером

Интерфейс позволяет с минимумом дополнительного оборудования подключаться к стандартным 16- или 32-разрядным микропроцессорным шинам. Интерфейс служит внешним портом, отображенным в адресное пространство, и обеспечивает асинхронную передачу данных.

Хост-процессор генерирует запрос шины. ADSP-2106x предоставляет шину по завершении текущего такта, выдавая сигнал предоставления шины и сигнал готовности. Хост-процессор может читать из памяти и записывать в память ADSP-2106x.

Обнаружение ошибок при передаче

В специальном управляющем регистре хранится информация о состоянии счетчика полубайтов каждого порта линка. Если по завершении передачи счетчик не обнулен, то вырабатывается сигнал, свидетельствующий об ошибке при передаче. Для контроля этого сигнала применяются специальные протоколы на передающем и принимающем концах линка.

В конце передачи блока слов передающий ADSP-2106x должен настроить свой порт на прием. Протокол обмена предусматривает передачу одного дополнительного пустого слова. Это позволит принимающему ADSP-2106x переслать соответствующее сообщение передающему. Протокол приема после получения блока данных предусматривает выработку прерывания для чтения управляющего регистра и передачи соответствующего сообщения передающему ADSP-2106x.

Микропроцессоры с архитектурой SHARC семейства ADSP-2116X;

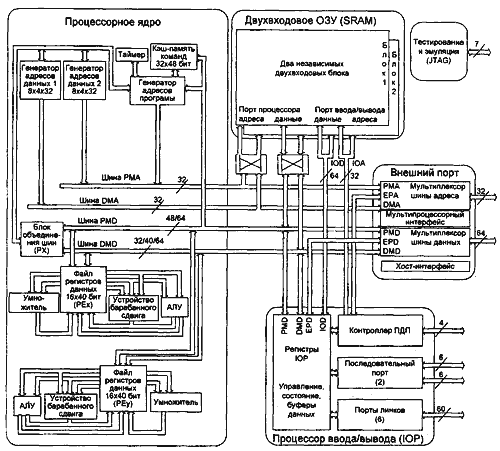

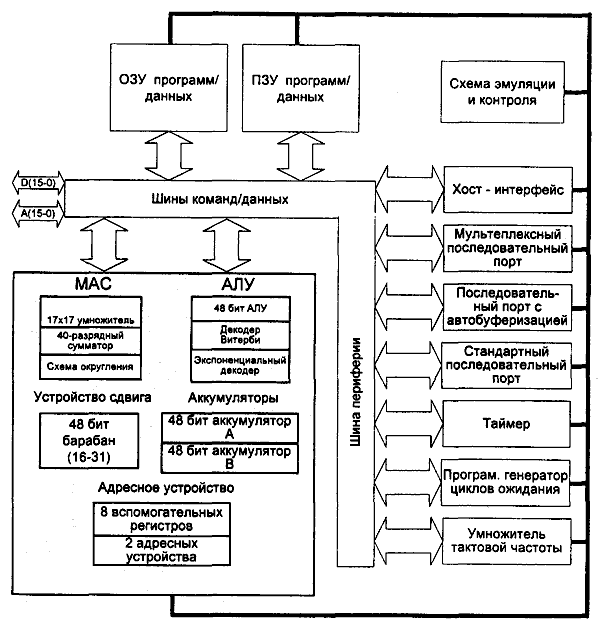

Следующей разработкой компании Analog Devices явились 32-разрядные микропроцессоры семейства SHARC - ADSP-2116x, представленные в 1998 году.

Основным отличием семейства ADSP-2116x от ADSP-2106x является наличие в составе микропроцессорного ядра двух процессорных элементов. Процессорные элементы могут одновременно выполнять команду, каждый над своими данными (режим SIMD). SIMD-обработка данных позволяет существенно увеличить производительность микропроцессора при незначительном изменении программной модели. Отличием от микропроцессоров предыдущей серии является также увеличенная разрядность внутренних шин.

Каждый процессорный элемент содержит набор обрабатывающих устройств: 32-, 40-разрядное арифметико-логическое устройство с фиксированной и плавающей точкой, 32-, 40-разрядный умножитель в формате с плавающей точкой с 80-разрядным регистром-аккумулятором, устройство барабанного сдвига, регистровый файл - 32 40-разрядных регистра.

Структура микропроцессора ADSP-2116x показана на рис. 8.

Рис. 8. Структура микропроцессора ADSP-2116x

Новая серия микропроцессоров программно совместима с ADSP-2106x на уровне исполняемых кодов. Система программирования ADSP-2116x - ADI Visual DSP - включает трансляторы, отладчики, оптимизированные библиотеки, а также аппаратные средства поддержки разработки.

Микропроцессор ADSP21160 является первым представителем новой серии. Он содержит 4 Мбит внутренней памяти, 14 каналов ПДП, 6 линков. Приведем основные характеристики данного микропроцессора:

При относительно небольшой тактовой частоте высокая реальная производительность микропроцессоров ADSP-2116x достигается благодаря эффективной системе команд. Например, программа КИХ-фильтрации для микропроцессора TMS320C67x содержит 100 команд, тогда как программе для ADSP-2116x требуется всего 25 команд.

В табл. 2 приведены результаты тестирования микропроцессоров семейства SHARC на распространенных алгоритмах ЦОС.

Таблица 2. Производительность микропроцессоров семейства SHARC

|

ADSP-21065L SHARC |

ADSP-21160 SISD |

ADSP-21160 SIMD |

|

|

Тактовая частота |

66 МГц |

100 МГц |

100 МГц |

|

Длительность такта |

15 нс |

10 нс |

10 нс |

|

Mflops средняя |

132 Mflops |

200 Mflops |

400 Mflops |

|

Mflops пиковая |

198 Mflops |

300 Mflops |

600 Mflops |

|

Комплексное БПФ на 1024 точки |

274 мкс |

180 мкс |

90 мкс |

|

Звено КИХ-фильтра |

15 нс |

10 нс |

5 нс |

|

Звено БИХ-фильтра |

60 нс |

40 нс |

20 нс |

|

Умножение матриц: |

|||

|

[3x3]* [3x1] |

135 нс |

90 нс |

45 нс |

|

[4x4]* [4x1] |

240 нс |

160 нс |

80 нс |

|

Деление |

90 нс |

60 нс |

30 нс |

|

Извлечение квадратного корня |

135 нс |

90 нс |

45 нс |

Пути дальнейшего повышения производительности компания Analog Devices связывает со статическим выявлением параллелизма уровня команд. ADSP-TS001 - первый микропроцессор семейства TigerSHARC с новой статической суперскалярной архитектурой. Процессоры TigerSHARC сочетают возможности цифровой обработки сигналов с особенностями RISC и VLIW.

В ADSP-TS001 поддерживаются на высоком уровне такие присущие процессорам ЦОС характеристики, как короткий машинный такт с детерминированной длительностью, быстрая реакция на прерывания и эффективный интерфейс с периферийными устройствами. Это достигается использованием VLIW-подхода к планированию загрузки функциональных блоков (выявление параллелизма уровня команд на этапе компиляции и возможность независимого задания в программе порядка загрузки функциональных блоков) и RISC-подхода к исполнению команд (фиксированная структура команды, конвейерное выполнение за один такт до четырех 32-разрядных операций над данными в регистровом файле, предсказание переходов и т. д.). Работая на тактовой частоте 150 МГц, процессор ADSP-TS001 обеспечивает наибольшую производительность среди процессоров семейства SHARC как при обработке данных с фиксированной точкой, так и при работе с данными в формате с плавающей точкой. ADSP-TS001 может обрабатывать 8-, 16-, 32-разрядные типы данных с фиксированной и плавающей точкой, причем скорость обработки увеличивается при уменьшении разрядности данных.

Рассмотрим основные характеристики микропроцессора ADSP-TS001.

Производительность:

Память:

Коммуникационные возможности:

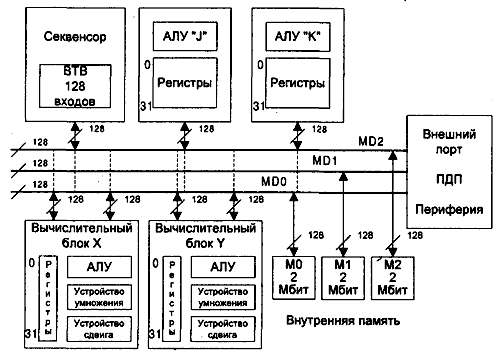

Внутренняя структура процессора TigerSHARC показана на рис. 9.

Рис. 3.25. Структура микропроцессора ADSP-TS001

В состав микропроцессора входят: вычислительные блоки, память, 2 АЛУ адресной арифметики, блок формирования последовательности команд (секвенсор) и периферийные компоненты.

Каждый из вычислительных блоков X и Y содержит 32-регистровый файл, умножитель, АЛУ и 64-разрядное устройство сдвига.

Эффективная загрузка функциональных устройств микропроцессора, планируемая в соответствии с VLIW-подходом на стадии компиляции программы, позволяет процессору в одном такте выполнять восемь 40-разрядных операций умножения с накоплением 16-разрядных данных, две 40-разрядных операции умножения с накоплением 16-разрядных комплексных чисел или две 80-разрядные операции умножения с накоплением 32-разрядных данных.

Два АЛУ (J, К) предназначены для вычисления адресов, но могут быть использованы и для выполнения целочисленных операций над данными. Каждое АЛУ имеет свой 32-регистровый файл, поддерживает циклические буферы и бит-реверсивную адресацию.

Секвенсор обеспечивает порядок исполнения команд, при котором каждая очередная команда выполняется в соответствии с результатом предварительно заданного условия. Кроме того, одна и та же команда может быть выполнена двумя вычислительными блоками одновременно с использованием различных значений данных (SIMD-обработка).

Для уменьшения потерь производительности, связанных с необходимостью перезагрузки исполнительных конвейеров в случае выполнения переходов, в микропроцессоре используются буфер адресов перехода (ВТВ - Branch Target Buffer) и статическое предсказание переходов.

Внутренняя и внешняя память микропроцессора организованы в виде единого адресного пространства. Внутренняя память разделена на три 128-разрядных блока по 2 Мбит каждый, что позволяет при обращении к памяти читать из нее в регистровый файл учетверенные, длинные и нормальные слова, выбирать в каждом цикле до четырех 32-разрядных команд. Одновременно может быть загружено в регистровый файл или записано в память 256 битн данных. Данные с длиной слова 8, 16 или 32 разряда могут записываться в память последовательно в упакованном виде. При работе на тактовой частоте 150 МГц скорость обмена с внутренней памятью составляет 7,2 Гбит/с.

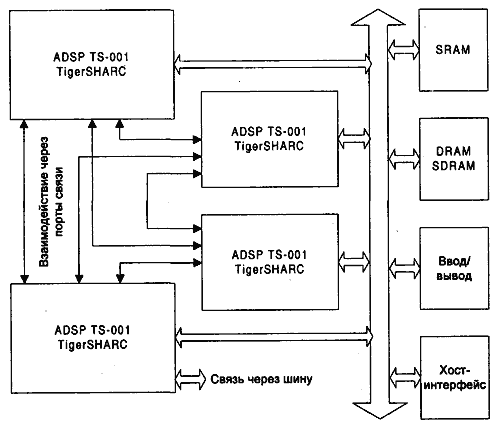

Шинная структура микропроцессора обеспечивает возможность одновременной передачи двух операндов результата. Три 128-разрядные шины образуют быстродействующий канал передачи данных между внутренними функциональными блоками и внешними периферийными устройствами. Высокоскоростной 64-разрядный интерфейс внешней шины позволяет строить на базе ADSP-TS001 мультипроцессорные системы, объединяющие до 8 процессоров. На рис. 10 показана одна из возможных подобных систем.

Рис. 10. Использование ADSP-TS001 в многопроцессорных системах

Наряду с внешней шиной, для взаимодействия между процессорами могут использоваться порты связи. Передача данных через порты связи выполняется отдельным процессором ввода/вывода и не требует вмешательства ЦП. Данный способ не имеет ограничений по числу взаимодействующих процессоров и обладает большей гибкостью, однако обеспечивает меньшую пропускную способность.

При производстве следующих микропроцессоров семейства TigerSHARC планируется использовать меньшие технологические нормы, что позволит увеличить тактовую частоту. Кроме этого, разные представители семейства будут различаться объемами встроенной памяти и составом интегрированных периферийных устройств.

Основная область применения микропроцессоров TigerSHARC - телекоммуникации, требующие высокопроизводительной обработки данных: базовые станции сотовых сетей третьего поколения, приложения, связанные с передачей речи по сетям с протоколом TCP/IP (VoIP - Voice over IP), серверы и сетевые концентраторы.

Микропроцессор ADSP-21535 - первый представитель семейства микропроцессоров Blackfin, с микросигнальной архитектурой, разрабатываемой совместно компаниями Analog Devices и Intel. Процессор выпускается с начала 2002 года в двух вариантах: ADSP-21535PKB-300 (для частоты 300 МГц) и ADSP-21535PKB-200 (для частоты 200 МГц).

Особенностью данной архитектуры является сочетание в одном микропроцессоре возможностей сигнальной обработки, SIMD-обработки мультимедийных данных и RISC-подобного набора команд.

ADSP-21535 отличает чрезвычайно низкое энергопотребление при достаточно высокой производительности и широком наборе интегрированных периферийных устройств.

Производительность микропроцессора на операции "умножение с накоплением" (MAC) составляет: при частоте 300 МГц - 600 MMACS, при частоте 200 МГц - 400 MMACS.

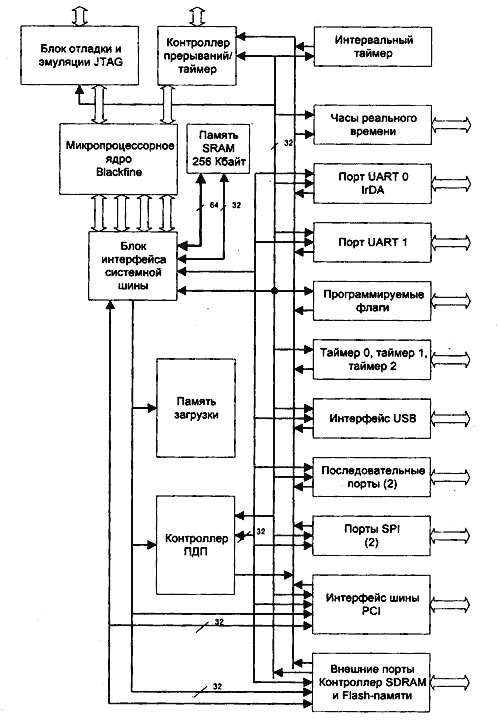

На кристалле (рис. 11) помимо микропроцессорного ядра содержатся 256 Кбайт статической памяти, контроллер ПДП, контроллер прерываний, блок интерфейса системной шины, память загрузки, таймеры, контроллер внешней памяти, контроллер шины PCI, интерфейс USB, универсальный асинхронный интерфейс (UART - Universal Asynchronous Receiver/Transmitter) блок эмуляции и отладки JTAG.

Рис. 11. Структура микропроцессора Blackfin

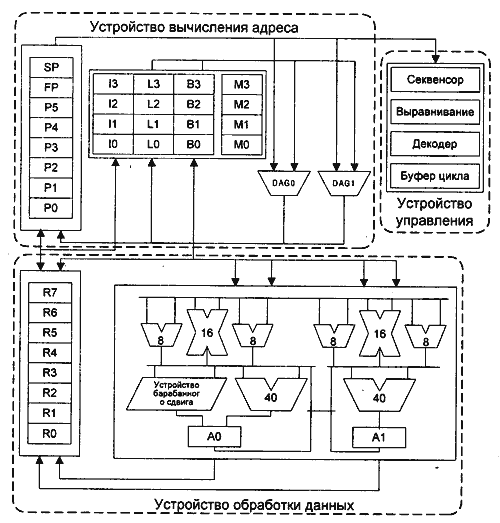

Ядро ADSP-21535 состоит из 3 компонентов: устройство вычисления адреса, устройство управления и устройство обработки данных (рис. 12).

Рис. 12. Ядро микропроцессора Blackfin

Устройство вычисления адреса содержит два генератора адреса (DAG0 и DAG1), использующие общий регистровый файл. Регистровый файл включает 4 набора регистров: индексный, модификатор, длины, базы. Восемь дополнительных 32-разрядных регистров могут использоваться совместно с основными индексными регистрами в качестве указателей позиций стека и памяти.

Устройство управления содержит блок формирования последовательности команд (Sequencer), блоки выделения и декодирования команд, а также буфер команд цикла (для локального сохранения команд в целях сокращения числа обращений к памяти команд).

Устройство обработки данных содержит 9 вычислительных устройств: 2 блока выполнения операций умножения с накоплением (MAC), два 40-разрядных АЛУ, четыре видео-АЛУ и устройство барабанного сдвига. Вычислительные устройства обрабатывают 8-, 16- или 32-разрядные данные, содержащиеся в регистровом файле.

Каждая команда MAC осуществляет умножение 16-разрядных данных за один процессорный такт с формированием 40-разрядного результата. Каждое АЛУ может выполнять стандартный набор арифметических и логических операций, большинство из которых выполняется за один процессорный такт. Содержимое восьми 32-разрядных регистров может интерпретироваться АЛУ как 32-разрядные данные или как пара 16-разрядных данных. За один процессорный такт 2 АЛУ могут вычислять до 4 результатов операций над 16-разрядными данными.

Устройство барабанного сдвига может выполнять простые и циклические сдвиги, нормализацию над 40-разрядным операндом, извлечение и хранение данных.

В микропроцессоре реализована модифицированная гарвардская архитектура в комбинации с иерархической структурой памяти. Вся память микропроцессора рассматривается как унифицированное адресное пространство размером до 4 Гбайт.

Первый уровень иерархии памяти работает на частоте ядра и имеет минимальное время доступа. Память команд этого уровня (16 Кбайт на кристалле) содержит только команды. Память данных первого уровня иерархии (два банка по 16 Кбайт на кристалле) содержит, наряду с данными, стек и локальные переменные. К этому же уровню иерархии относится и внутренняя память промежуточных результатов (scratchpad) размером 4 Кбайт. Память первого уровня может быть сконфигурирована как быстрая память прямого доступа или как кэш-память (за исключением scratchpad).

Второй уровень иерархии памяти - это внутренняя (256 Кбайт SRAM) и внешняя память, доступ к которой осуществляется за несколько процессорных тактов. Память этого уровня является общей для команд и данных.

Большое внимание при создании микропроцессоров семейства Blackfin разработчики уделили сокращению энергопотребления. В них реализовано гибкое динамическое управление питанием: в зависимости от интенсивности вычислений изменяется напряжение питания и тактовая частота работы микропроцессора.

Дальнейшее развитие семейства идет в направлении повышения производительности, сокращения энергопотребления и использования проблемно-ориентированного набора периферии.

К другим представителям семейства Blackfin относятся:

Новые Blackfin-процессоры поддерживают встраиваемые операционные системы, такие как Linux Embedded, ThreadX и Nucleus.

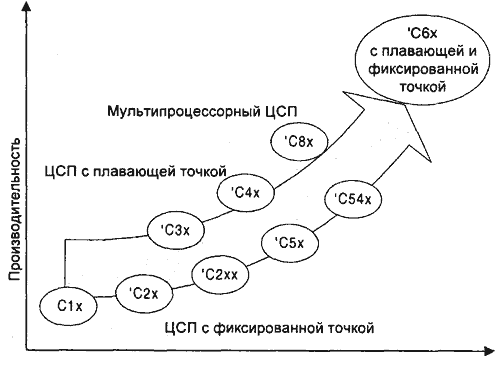

Сигнальные процессоры компании Texas Instruments разделяются на два класса: процессоры для обработки чисел с фиксированной точкой и процессоры для обработки чисел с плавающей точкой (рис. 1). Первый класс представлен тремя семействами процессоров, базовыми моделями которых являются соответственно TMS320C10, TMS320C20, TMS320C50. Второй класс включает процессоры TMS320C30, TMS320C40. TMS320C80 также поддерживает операции с плавающей точкой и представляет собой мультипроцессорную систему, выполненную в одном кристалле, а семейство TMS320C6x включает процессоры как с фиксированной, так и с плавающей точкой.

Рис 1. Семейства микропроцессоров компании TI

Процессоры старших поколений одного семейства наследуют основные архитектурные особенности предшествующих поколений и совместимы "снизу вверх" по системе команд (чего нельзя сказать о процессорах, входящих в разные семейства).

Первый процессор семейства - TMS320C10 - был выпущен в 1982 году и, благодаря ряду удачных технических решений, получил широкое распространение. Структура типичного представителя семейства - микропроцессора TMS320C15 - приведена на рис. 2.

Рис. 2. Структура микропроцессора семейства TMS320C1X

В основу микропроцессора положена модифицированная гарвардская архитектура, отличием которой от традиционной гарвардской архитектуры является возможность обмена данными между памятью программ и памятью данных, что повышает гибкость устройства.

TMS320C10 является 16-разрядным процессором. Его адресное пространство составляет 4 Кслов памяти программ и 144 слова памяти данных. Все слои имеют разрядность 16. Длительность командного такта процессора составляет 160-200 нс.

Арифметические функции в процессоре реализованы аппаратно. Он имеет аппаратные умножитель (MULT), устройство сдвига (SHIFTER), aппаратную поддержку автоинкремента/декремента адресных регистров данных (AR0, AR1).

С внешними устройствами процессор взаимодействует через 8 портов ввода/вывода.

Каждый порт имеет разрядность 16. Предусмотрена возможность обработки внешних прерываний.

Другие микропроцессоры данного семейства (С14-С17) имеют аналогичную архитектуру и отличаются длительностью командного такта, конфигурацией памяти, наличием (или отсутствием) дополнительных периферийных устройств (например, в С17 реализованы кодек данных по мю-/А-закону, преобразователь логарифмической импульсно-кодовой модуляции (ИКМ) в линейную ИКМ).

Микропроцессоры семейства TMS320C2x имеют ту же архитектуру, что и TMS320C1x, но обладают более высокой производительностью и более широкими функциональными возможностями. Все процессоры семейства могут использовать по 64 Кслов памяти программ и данных, имеют 16 портов ввода/вывода каждый разрядностью 16 и последовательный порт.

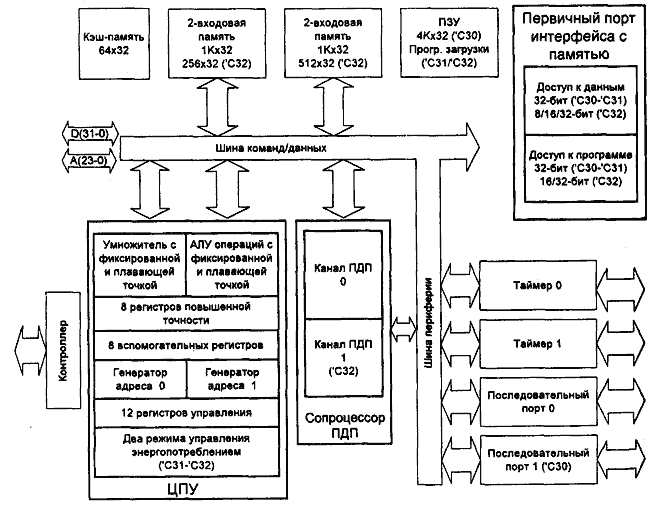

Структура микропроцессора TMS320C2x приведена на рис. 3.

Рис. 3. Структура микропроцессора TMS320C2x

Процессоры семейства TMS320C2x используют внешний контроллер прямого доступа в память (ПДП). Умножитель микропроцессоров помимо операций умножения позволяет выполнять за один такт возведение в квадрат. В процессоры включена аппаратная поддержка кратного выполнения команды, реализован режим двоичной инверсно-косвенной адресации, предназначенный для эффективной реализации быстрого преобразования Фурье.

Основные технические характеристики процессоров второго поколения приведены в табл. 1.

| Микропроцессор | Технология | Такт (нс) | Внутренняя память | Внешняя память | Ввод / вывод | ||||

| ОЗУ | ПЗУ | ППЗУ | Данных | Программ | Последовательный | Параллельный | |||

| TMS32020 | NMOS | 200 | 544 | 64К | 64К | 1 | 16x16 | ||

| TMS320C25 | CMOS | 100 | 544 | 4К | 64К | 64К | 1 | 16x16 | |

| TMS320C25-50 | CMOS | 80 | 544 | 4К | 64К | 64К | 1 | 16x16 | |

| TMS320E25 | CMOS | 100 | 544 | 4К | 64К | 64К | 1 | 16x16 | |

| TMS320C26 | CMOS | 100 | 1568 | 256 | 64К | 64К | 1 | 16x16 | |

Таблица 1. Основные характеристики процессоров семейства TMS320C2

Основные отличия архитектуры процессоров TMS320C2x от TMS320Clx за ключаются в следующем:

Процессоры следующего за TMS320C2x поколения, обеспечивая совместимость по системе команд и наследуя общие архитектурные особенности построения процессоров предыдущих поколений, отличаются от них большими функциональными возможностями, повышенной тактовой частотой, меньшим энергопотреблением.

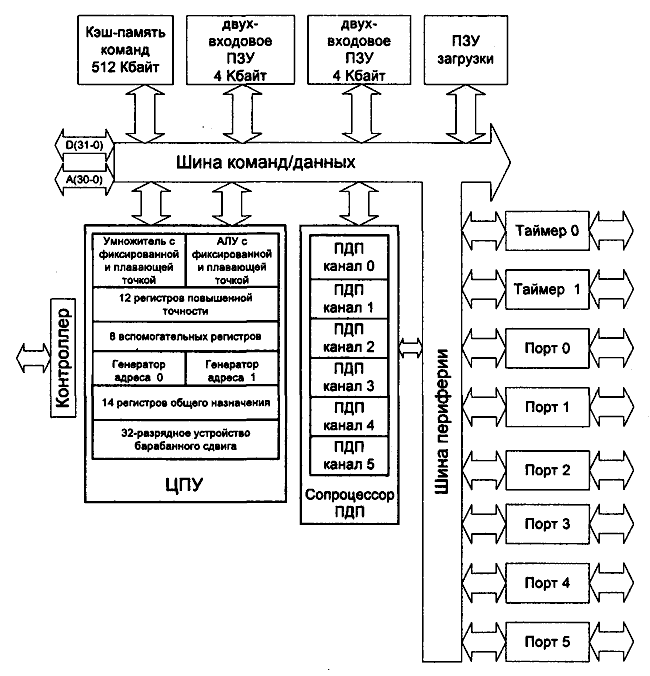

Структурная схема процессора TMS320C5x приведена на рис. 4.

Рис. 4. Структура микропроцессора TMS320C5x

В процессоре реализована аппаратная поддержка кольцевых буферов, имеется возможность одновременного создания в памяти данных двух независимых кольцевых буферов. Существует возможность кратного выполнения блока программы. Процессор содержит 11 теневых регистров, используемых для быстрого сохранения/восстановления состояния основных регистров в случае возникновения программных или аппаратных прерываний. Параллельное логическое устройство процессора позволяет выполнять битовые и логические операции над операндами, содержащимися в памяти и различных регистрах.

Процессор может использовать 244 Кслов памяти, в том числе: 64 Кслов - память программ, 64 Кслов - память данных, 64 Кслов - 16-разрядные порты ввода/вывода, 32 Кслов - глобальная память. Для возможности работы с медленной памятью в процессор включен программируемый генератор тактов ожидания. Для использования процессора в мультипроцессорных системах с разделяемой памятью в нем предусмотрены сигналы запроса и подтверждения готовности памяти. Различия между процессорами семейства TMS320C5x заключаются, в основном, в конфигурации внутрикристальной памяти.

Помимо 16-разрядных портов ввода/вывода, процессоры семейства имеют 2 последовательных порта (у TMS320C52 - 1), таймер, интерфейс тестирования и отладки JTAG.

Значительное внимание при разработке процессоров данного семейства уделялось обеспечению энергосберегающих режимов функционирования. Процессоры выпускаются на напряжение 3 В и 5 В. В микропроцессорах поддерживаются активный режим, периферийный режим и режим "сна". Потребление тока в активном режиме составляет 1,5 мА/MIPS на 3 В, 2,5 мА/MIPS на 5 В. В периферийном режиме центральный процессор останавливается, работает только периферия, и потребление тока составляет 0,25 мА/MIPS и 0,4 мА/MIPS для 3 и 5 В соответственно. В режиме "сна" процессор останавливается до получения сигнала прерывания. Потреблением тока составляет 5 мкА.

Архитектура TMS320C2xx базируется на архитектуре семейства TMS320C5x. Основные свойства микропроцессоров TMS320C2xx:

Модифицированная гарвардская архитектура, предусматривающая раздельные шины команд и данных, позволяет одновременно выбирать команды и операнды. Возможность обмена между памятью программ и данных увеличивает гибкость микропроцессора. Так, коэффициенты, расположенные в памяти программ, могут быть переданы в память данных, что приводит к экономии памяти, выделяемой для коэффициентов.

Процессор имеет увеличенный, по сравнению с предыдущими семействами, объем внутрикристальной памяти и перепрограммируемую энергонезависимую flash-память.

Наличие 4-этапного конвейера позволяет TMS320C2xx выполнять в среднем одну команду за такт. С2хх содержит средства управления прерываниями, повторного выполнения операций, вызова подпрограмм и функций.

Типовая структура микропроцессора С2хх приведена на рис 5.

Рис. 5. Структура микропроцессора TMS320C2xx

Все микропроцессоры семейства имеют одинаковое процессорное ядро и отличаются различными конфигурациями памяти и внутрикристальной периферией. Все устройства, кроме TMS320C209, имеют по 1 синхронному и 1 асинхронному последовательному порту.

Синхронный порт предназначен для обмена с другим процессором, кодеком и внешними периферийными устройствами. Порт имеет два буфера памяти емкостью по 4 слова с дисциплиной доступа FIFO и механизмом генерации прерываний. Максимальная скорость обмена через синхронный порт равна половине тактовой частоты процессора (для 40 МГц - скорость обмена 20 Мбит/с).

Асинхронный последовательный порт предназначен для обмена данными с другими устройствами. При обмене используется 8-битное представление данных с 1 стартовым и 1 или 2 стоповыми битами. Скорость обмена может достигать 250 тыс. 10-битных знаков в секунду.

Благодаря лучшему соотношению производительность/стоимость среди всех микропроцессорных семейств ($0,12 за MIPS), микропроцессоры TMS320C2xx получили самое широкое распространение и используются в связных системах, мультимедиа-устройствах, средствах промышленной автоматизации, военной технике.

Процессоры TMS320C54x отличает комбинирование модифицированной гарвардской архитектуры с тремя внутренними шинами данных и одной шиной команд. Такая внутренняя организация процессора позволяет обеспечить высокую степень параллельности выполнения команд. Этому семейству свойственна высокоспециализированная система команд, наличие на кристалле дополнительных периферийных устройств и увеличенный объем внутренней памяти. Все это позволяет добиться высокой гибкости и производительности.

Три шины данных используются для чтения операндов и записи результата операции одновременно с выборкой инструкции в одном процессорном цикле.

Общий объем адресуемой процессором памяти составляет 192 слова. Разрядность слов - 16. Память разбита на 3 специализированных сегмента: команд, данных и ввода/вывода, каждый из которых может иметь размер до 64 Кслов. В некоторых моделях внутри процессора может быть размешена ROM объемом до 48 слов и до 10 Кслов двухвходовой RAM. В процессоре предусмотрена опция защиты данных во внутренней памяти от сканирования. При установке режима защиты ни одна из команд не сможет получить доступ к содержимому внутрикристальной памяти.

Для ускорения выполнения типовых операций сигнальной обработки, помимо "стандартных" для процессоров ЦОС блоков барабанного сдвига и адресной арифметики, процессор содержит ряд дополнительных функциональных модулей, повышающих его гибкость и производительность. Блок умножения с накоплением (MAC) выполняет над 17-битными операндами операции вида S = S + а х b за один процессорный такт. Подобные операции характерны для алгоритмов фильтрации, свертки, вычисления корреля ционной функции.

Для быстрого вычисления значений у = ехр(х) микропроцессор содержит блок вычисления экспоненциальной функции. Этот блок, используя значение аккумулятора как значение аргумента функции х, позволяет вычислять соответствующее значение у = ехр(х) за один такт. Для эффективной реализаций оператора Витерби служит блок CMPS Operation, выполняющий за один цикл операцию сравнения/выбора с накоплением (Add/Compare Selection).

АЛУ микропроцессора способно выполнять арифметические или булевы операции над комплексными числами (используя два регистра аккумулятора - АССА и АССВ) или может функционировать как два 16 разрядных АЛУ, выполняющих одновременно две 16-разрядные операции. АЛУ и MAC могут реализовывать операции в цикле одновременно.

Устройство барабанного сдвига осуществляет сдвиг данных на 0 - 31 разрядов влево или 0 - 16 разрядов вправо за один такт, а также совместно с блокои вычисления экспоненциальной функции позволяет выполнять нормализацию содержимого аккумулятора за один такт. Дополнительные возможности сдвига позволяют процессору осуществлять масштабирование данных, выделять разряды числа, предотвращать возникновение переполнения и потери точности.

Все микропроцессоры семейства TMS320C54x имеют одинаковую структуру (рис. 6), однако отличаются друг от друга расположенной на кристалл периферией. В состав периферии входят:

Рис. 6. Структура микропроцессора TMS320C54x

Генератор тактов ожидания позволяет увеличить число тактов внешней шины для работы с медленной внешней памятью и внешними устройствами.

Переключатель банков памяти позволяет автоматически добавлять один такт при пересечении границ банка памяти внутри программного адресного пространства или при переходе от пространства адресов команд к пространству адресов данных. Этот дополнительный такт позволяет устройству памяти освободить шину раньше, чем другое устройство получит доступ к ней, избегая тем самым конфликтной ситуации при обращении к памяти.

Микропроцессоры семейства имеют 64 Кпорта ввода/вывода. Эти порты предназначены для связи с внешними устройствами с использованием минимума дополнительных внешних декодирующих схем. Интерфейс главного порта (HPI - Host Port Interface) - 8-разрядный параллельный порт, предназначенный для связи сигнального процессора и хост-процессора системы. Мы будем использовать термин "хост-процессор", т. к. представляется, что его замена на "главный процессор" или "управляющий процессор" не в полной мере адекватна. Обмен данными между хост-процессором и сигнальным процессором осуществляется через внутрикристальную HPI-память объемом 2 Кслов, разрядности 16, которая может также использоваться как память команд или данных. Скорость обмена по HPI составляет до 160 Мбайт/с.

Микропроцессоры семейства содержат высокоскоростные дуплексные последовательные порты, позволяющие связываться с другими микропроцессорами, кодеками и другими устройствами. В микропроцессоре реализованы следующие разновидности последовательных портов:

Универсальный последовательный порт использует два отображаемых в память регистра: регистр передачи данных и регистр приема данных. Передача и прием данных сопровождаются генерацией маскируемого прерывания, которое может быть обработано программно. Порт с разделением времени может обслуживать до семи устройств. Буферизированный последовательный порт позволяет осуществлять непосредственный обмен между устройством и памятью, не используя при передаче ресурсов процессора. Максимальная скорость обмена по последовательному порту может составлять до 40 Мбайт/с.

Как и в семействах TMS320C5x, TMS320C2xx, в процессоре реализована эффективная трехуровневая система управления энергопотреблением.

Высокая производительность (до 66 MIPS) и расширенные функциональные возможности при невысокой цене обеспечивают процессору обширные области применения: сотовые и радиотелефоны, персональные системы радиовызова, карманные персональные компьютеры (PDA - Personal Digital Assistant), устройства беспроводной передачи данных (радиосети) и т. д.

Первым представителем класса процессоров с плавающей точкой стал TMS320C30. На момент выпуска процессора - в конце 1980 годов - TMS320C30 значительно превосходил по производительности процессоры других компаний - производителей сигнальных процессоров. Процессор имеет гибкую систему команд, хорошую аппаратную поддержку операций с плавающей точкой, мощную систему адресации, расширенное адресное пространство, обеспечивает поддержку выполнения конструкций языка высокого уровня - С на аппаратном уровне.

Процессор производился по 0,7 мкм КМОП-технологии с тремя уровнями металлизации. Все операции в процессоре выполняются за один такт. При длительности такта 60 нс процессор TMS320C30 имеет быстродействие около 33 Mflops. Высокая производительность процессора на алгоритмах ЦОС обеспечивается благодаря аппаратному выполнению ряда специфических функций, которые в других процессорах реализуются программно или микропрограммно. Процессор имеет конвейерную регистро-ориентированную архитектуру и может параллельно выполнять в одном такте умножение и арифметико-логические операции с числами в формате с фиксированной или плавающей точкой. Структура процессора приведена на рис. 7.

Рис 7. Структура микропроцессора TMS320C30

Процессор имеет 32-разрядную шину команд и данных и 24-разрядную шину адреса. Содержит 2 блока ОЗУ по одному 32-разрядному Кслову, 32-разрядный умножитель с плавающей точкой, кэш-память команд объемом 64 слова (32-разрядных), 8 регистров для операций с повышенной точностью, 2 генератора адреса и регистровый файл. В процессоре реализованы разнообразные методы адресации. 40-разрядное АЛУ процессора работает как с целыми числами, так и с числами в формате с плавающей точкой. Встроенный контроллер ПДП позволяет совмещать во времени вычисления и выполнение обменов данными с памятью. Наличие у TMS320C30 мультипроцессорного интерфейса, двух внешних интерфейсных портов, двух последовательных портов, расширенной системы прерываний упрощает конструирование систем на его основе. Благодаря своей высокой производительности и простоте использования в вычислительных системах TMS320C30 может применяться как в качестве хост-процессора, так и в качестве специализированного сопроцессора.

Процессоры СЗх отличаются, в основном, количеством последовательных портов (С31 и С32 - 1, С30 - 2) и каналов ПДП (СЗ0, С32, - 2, С31 - 1).

Представители этого семейства получили большую популярность у разработчиков. Учитывая значительный объем программных наработок для микропроцессоров TMS320C3x, Texas Instruments в последствии повторно выпустила это семейство, но уже по новой технологии 0,18 мкм, с увеличенной внутренней памятью (34 Кслов), повышенной тактовой частотой и меньшим энергопотреблением. Производительность обновленного микропроцессора составила 150 Mflops.

Основными областями применения микропроцессоров семейства СЗх являются: цифровое аудио, ЗD-графика, видеоконференцсвязь, промышленные роботы, копировально-множительная техника, телекоммуникационные системы.

Следующими представителями сигнальных процессоров с плавающей точкой явились процессоры семейства TMS320C4x.

Благодаря своей уникальной архитектуре микропроцессоры TMS320C4x получили широкое распространение в мультипроцессорных системах и практически вытеснили ранее господствующее в этой технологической нише семейства транспьютеров компании Inmos.

Процессоры TMS320C4x совместимы по системе команд с TMS320C3x, однако обладают большей производительностью и лучшими коммуникационными возможностями.

В семейство TMS320C4x входят процессоры TMS320C40, TMS320C44, TMS320LC40.

TMS320C40 - имеет производительность 30 MIPS/60 Mflops и максимальную пропускную способность подсистемы ввода/вывода 384 Мбайт/с. С40 содержит на кристалле 6 высокоскоростных (20 Мбайт/с) коммуникационных портов и 6 каналов ПДП, 2 Кслов памяти, 128 слов кэш-памяти программ и начальный загрузчик. Две внешних шины обеспечивают работу с 4 Гслов объединенного адресного пространства.

Процессор TMS320C44 - более дешевый вариант, имеющий 4 коммуникационных порта и адресуемое пространство 32 Мслов. Однако значения показателей производительности и пропускной способности процессора те же, что и у С40.

TMS320LC40 - архитектурный аналог TMS320C40, отличающийся низким энергопотреблением, повышенной производительностью (40 MIPS/80 Mflops) и большей пропускной способностью (488 Мбайт/с).

Структура микропроцессора TMS320C40 приведена на рис. 8.

Рис. 8. Структура микропроцессора TMS320C40

Центральный процессор TMS320C4x имеет конвейерную регистро-ориентированную архитектуру. Компонентами ЦП являются:

Умножитель выполняет операции над 32-разрядными данными в формате с фиксированной точкой и 40-разрядными данными в формате с плавающей точкой, причем умножение производится за один такт (25 нч) для данных любого типа и параллельно с обработкой данных в других функциональных блоках микропроцессора (например, АЛУ).

АЛУ выполняет за один такт операции над 32-разрядными целыми и логическими данными и 40-разрядными числами в формате с плавающей точкой, в том числе и операции преобразования форматов представления данных. Микропроцессор аппаратно поддерживает операции деления и извлечения квадратного корня. Устройство барабанного сдвига позволяет за один такт выполнить сдвиг данных влево или вправо на число позиций от 1 до 32.

Два дополнительных модуля регистровой арифметики (генераторы адреса) функционируют параллельно с умножителем и АЛУ и могут генерировать два адреса в одном такте. В процессоре поддерживается относительная базовая, базово-индексная, циклическая и бит-реверсивная адресации.

Первичный регистровый файл центрального процессорного устройства (ЦПУ) представляет собой многовходовый файл из 32 регистров. Все регистры первичного регистрового файла могут использоваться умножителем, АЛУ и в качестве регистров общего назначения. Регистры имеют некоторые специальные функции. Например, 12 регистров повышенной точности могут использоваться для размещения результатов операций с плавающей точкой, 8 дополнительных регистров - для некоторых косвенных способов адресации, а также как целочисленные и логические регистры общего назначения. Остальные регистры обеспечивают функции системы такие, как адресация, управление стеком, прерывания, отображение статуса процессора, повторы блоков команд.

Регистры повышенной точности предназначены для хранения и обработки 32-разрядных целых чисел и 40-разрядных чисел с плавающей точкой. Дополнительные регистры доступны как для АЛУ, так и для двух модулей адресной арифметики. Основная функция этих регистров - генерация 32-разрядных адресов. Они также могут использоваться как счетчики циклов или как регистры общего назначения.

Адресуемое микропроцессором пространство составляет 4 Гслов 32-разрядных. На кристалле расположены два двухвходовых блока оперативной памяти RAM0 и RAM1 размером 4 Кбайт каждый, а также двухвходовый блок ROM, содержащий программу начальной загрузки.

Кэш-память команд процессора емкостью 128 слов (32-разрядных) содержит наиболее часто используемые участки кода, что позволяет сократить среднее время выборки команд. Высокая производительность TMS320C4x достигается благодаря внутреннему параллелизму процессов и многошинной организации процессора. Раздельные шины позволяют одновременно выполнять выборку команды, данных и прямой доступ в память.

Шесть (С44 четыре) высокоскоростных (160 Мбит/с) коммуникационных портов обеспечивают эффективный обмен данными между процессорами. В ходе передачи осуществляется буферизация передаваемых и принимаемых данных и автоматический контроль за синхронизацией всех обменных операций между каналами, центральным процессором и сопроцессором ПДП. Шесть каналов сопроцессора ПДП содержат собственные генераторы адресов, счетчики, входные и выходные регистры и обеспечивают возможность одновременного бесконфликтного обращения к памяти, обмена данными с медленными модулями памяти и внешними устройствами, без снижения производительности процессора. Особенностью сопроцессора ПДП является способность автоматической инициализации каналов после выполнения обмена.

Линк Ly, у = 0, ..., 5, состоит из 8-разрядной двунаправленной линии данных Dу (7-0) и двунаправленных одноразрядных управляющих линий для передачи сигналов:

Линии данных и управляющие линии реализованы как двунаправленные, что приводит к необходимости согласования состояний портов линков, соединяющих два микропроцессора: один порт обязательно передающий, другой - принимающий, либо оба порта находятся в третьем состоянии, исключающем передачу электрических сигналов между ними. При начальной установке обязательно выполнение этого требования, которое дальше поддерживается протоколом функционирования линка. Передающий порт отмечается маркером, который передается другому порту при смене направления передачи по линку. Передача маркера происходит за 4 такта.

Очереди портов

Каждый порт имеет входную и выходную FIFO-очереди. Процессор или канал ПДП пересылают данные в конец выходной FIFO-очереди порта для передачи их по линку. Выборка принятых данных выполняется из начала входной FIFO-очереди. Обе очереди имеют по 8 элементов, каждый из которых предназначен для хранения 32-битного слова. При соединении двух С4х в каждом линке образуется очередь в 16 элементов: 8 элементов на одном конце линка и 8 элементов на другом конце линка.

Интерфейс линков

Программное управление передачами данных по линкам выполняется путем записи соответствующих кодов в регистры состояния и управления линков. Для каждого линка в С4х выделена часть адресного пространства размером 16 слов:

Поля и отдельные биты управляющего регистра определяют:

Функционирование линков

Когда функционирование порта как входного прекращено, он не дает сигнала готовности к приему после получения первого байта. Передача данных останавливается до момента переключения порта в режим входного порта или до поступления сигнала сброса. При этом передача данных после возобновления идет без потери байтов.

Коммуникационный порт не выдает подтверждения на запрос маркера в следующих случаях:

При этом порт, сохранив маркер, может функционировать как выходной.

Если коммуникационный порт прекращает функционировать в качестве входного порта в момент приема запроса маркера, то подтверждение на запрос маркера выдается до остановки.

Прекращение функционирования порта как выходного приводит к следующим последствиям:

Основной механизм синхронизации базируется на сигналах "готов/не готов". Если канал прямого доступа в память или центральный процессор пытаются прочитать из пустой входной очереди или записать в полную выходную очередь, выдается сигнал "не готов" и каналы ПДП или ЦП продолжат чтение или запись после получения сигнала "готов".

Сигналом готовности для выходного канала является OCRDY (Output Channel Ready), который также является сигналом прерывания. Сигналом готовности для входного канала является ICRDY (Input Channel Ready), который также является сигналом прерывания.

Каждый порт способен генерировать четыре различных сигнала прерывания:

ЦП может обрабатывать все 4 сигнала, а канал ПДП только сигналы готовности.

Два 32-разрядных таймера могут работать как с внутренней, так и с внешней синхронизацией, осуществлять подсчет временных интервалов и внешних событий, выдавая сигналы процессору или во внешнюю среду.

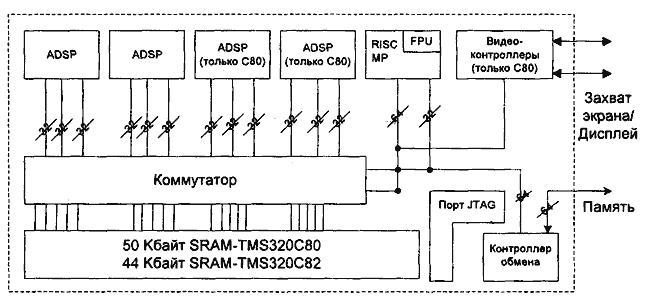

Микропроцессор TMS320C80, выпущенный в конце 1994 года, имеет второе название - MVP (Multimedia Video Processor - мультимедийный видеопроцессор), что обусловлено его высокой эффективностью на задачах обработки изображений, в системах виртуальной реальности, компрессии и декомпрессии видео- и аудиоданных, обработки связной информации.

TMS320C80 представляет собой новый подход к повышению производительности и функциональности цифровых сигнальных процессоров: в одной микросхеме объединено четыре усовершенствованных цифровых процессора обработки сигналов (ADSP - Advanced Digital Signal Processor), каждый из которых выполняет за такт несколько RISC-операций, и пятый процессор, называемый главным процессором (Master Processor - МР), - 32-разрядный процессор с высокопроизводительным устройством обработки чисел в формате с плавающей точкой. В дополнение к процессорному ядру на кристалле размещены:

Выпускается также упрощенный вариант микропроцессора TMS320C82, который отличается меньшим объемом памяти, количеством сигнальных процессоров ADSP (2), отсутствием видеоконтроллера и, соответственно, меньшей стоимостью.

Структура процессора изображена на рис. 9.

Рис. 9. Структура микропроцессора TMS320C8X

Суммарная производительность TMS320C80 на регистровых операциях достигает 2 млрд RISC-подобных команд в секунду. Благодаря столь высокой производительности TMS320C80 может заменить при реализации ряда приложений более 10 высокопроизводительных сигнальных микропроцессоров или универсальных микропроцессоров, выпускавшихся до его появления.

Приведем технические характеристики TMS320C80:

Архитектура микропроцессора TMS320C80

Архитектура процессора TMS320C80 относится к классу MIMD - множественный поток данных, множественный поток команд. Входящие в состав TMS320C80 процессоры программируются независимо один от другого и могут выполнять как разные, так и одну общую задачу. Обмен данными между процессорами осуществляется через общую внутрикристальную память, доступ к которой обеспечивает матричный коммутатор (Crossbar), выполняющий также функции монитора при одновременном обращении к одному сегменту памяти нескольких процессоров.

Рассмотрим подробнее архитектуру процессоров, входящих в состав TMS320C80.

Архитектура главного процессора

Главный процессор - это вычислительное устройство с RISC-архитектурой и встроенным сопроцессором для выполнения операций с плавающей точкой. Подобно другим процессорам с RISC-архитектурой, МР использует команды загрузки/сохранения для доступа к данным в памяти, а также выполняет большинство целочисленных, битовых и логических команд над операндами в регистрах в течение одного такта.

Вычислитель с плавающей точкой (FPU - Floating Point Unit) конвейеризирован и позволяет выполнять операции над данными как с одинарной, так и с двойной точностью, совмещая в конвейере операции умножения, сложения с накоплением, загрузки и сохранения результата. FPU использует тот же регистровый файл, что и устройство целочисленной и логической обработки. Производительность устройства составляет около 100 Mflops. Специальный механизм отметок (Scoreboard) фиксирует занятость регистров и обеспечивает их бесконфликтное использование.

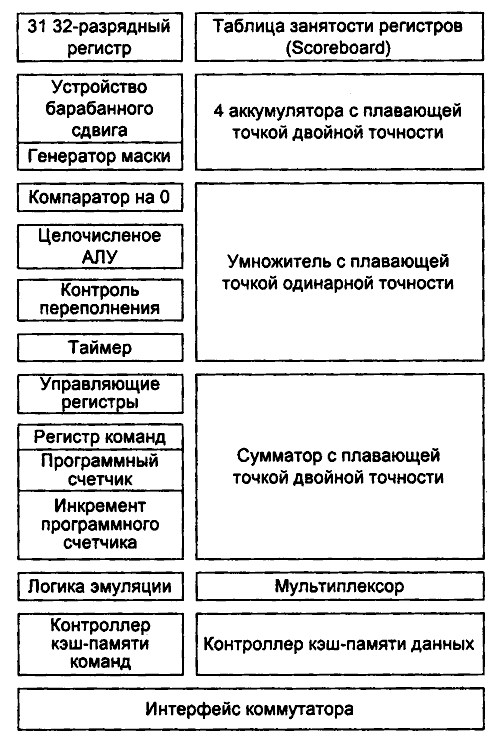

На рис. 10 приведена структура главного процессора.

Рис. 10. Структура главного процессора

Основными компонентами МР являются:

Объем каждого из внутрикристальных кэшей МР для команд и данных равен 4 Кбайта. Управление кэш-памятью осуществляет входящий в состав МР контроллер.

МР может обслуживать до четырех внешних прерываний. Запрос на обслуживание трех из них должен иметь форму импульса, а для одного - передача управления процедуре обработки осуществляется по изменению уровня напряжения.

Для различных схем распараллеливания обработки в рамках микропроцессора МР может использоваться как управляющий или как универсальный арифметико-логический и графический процессор.

Набор инструкций МР включает в себя:

Архитектура ADSP-процессоров

Архитектура ADSP-процессоров TMS320C80 оптимизирована для приложений, связанных с обработкой 2- и 3-мерной графики, видеоизображений и звука. ADSP может выполнять за один такт одновременно операцию умножения, арифметико-логическую операцию (например, сдвиг-суммирование) и два обращения к памяти. Внутренний параллелизм ADSP позволяет обеспечить на некоторых алгоритмах быстродействие свыше 500 млн операций в секунду.

ADSP манипулирует 32-разрядными словами, а разрядность команд составляет 64 бита. Процессор использует прямую, непосредственную и 12 видов косвенной адресации.

Архитектура ADSP характеризуется следующими параметрами:

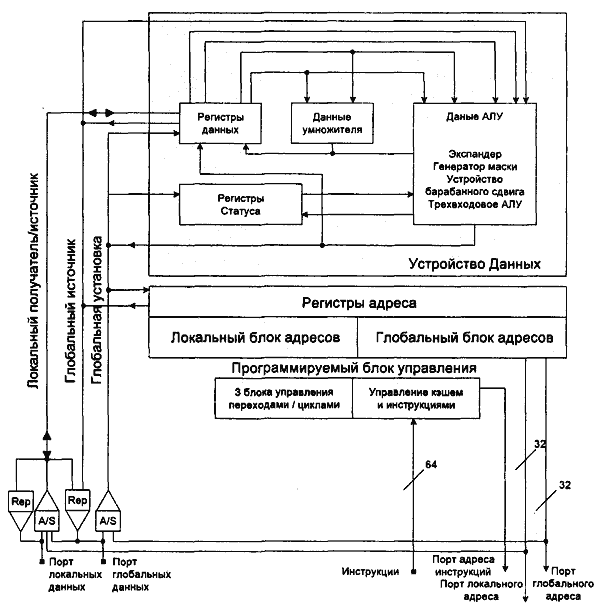

Структура ADSP-процессора показана на рис. 11.

Рис. 11. Структура ADSP-процессора

На рисунке обозначены:

Контроллер обмена

Контроллер обмена управляет операциями обмена процессоров и памяти как внутри кристалла (через коммутатор), так и вне кристалла, с использованием входящих в его состав интерфейсных схем, поддерживающих все распространенные стандарты памяти (DRAM, VRAM, SRAM) и обеспечивающих возможность динамического изменения разрядности шины от 8 до 64. Используя приоритетную дисциплину обслуживания запросов к памяти в режиме ПДП, контроллер обмена позволяет выполнять обмен данными, не прерывая вычислений со скоростью до 400 Мбайт/с.

Контроллер обмена поддерживает линейную и координатную адресацию памяти для эффективного выполнения обмена при работе с 2- и 3-мерными графическими изображениями.

Видеоконтроллеры

Два расположенных на кристалле микропроцессора TMS320C80 видеоконтроллера обладают возможностью захвата и отображения видеоинформации в режимах как вертикального, так и горизонтального сканирования. Режимы захвата/сканирования могут устанавливаться для каждого из контроллеров независимо.

Области применения микропроцессора TMS320C80

Области применения микропроцессора гораздо шире тех, что обозначены его названием. Процессор нашел свое применение в системах: обработки мультимедийной информации, видеоконференцсвязи, обработки 2- и 3-мерной графики, моделирования виртуальной реальности, передачи данных.

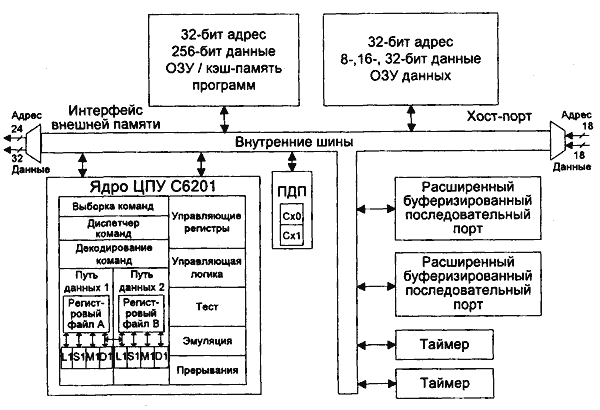

Новое семейство процессоров ЦОС компании Texas Instruments - TMS320C6x - включает в себя процессоры как с фиксированной, так и с плавающей точкой. Первый представитель данного семейства TMS320C6201 оперирует с данными только в формате с фиксированной точкой.

На тактовой частоте 200 МГц микропроцессор имеет производительность до 1,6 млрд операций в секунду. Областями его применения являются:

TMS320C6201 помимо процессорного ядра содержит:

Построенный в соответствии с разработанной компанией Texas Instruments архитектурой VelociTI, процессор С62хх - первый из сигнальных VLIW-процессоров, использующий для повышения производительности параллелизм уровня команд.

Структура микропроцессора TMS320C6201 приведена на рис. 12.

Рис. 12. Структура микропроцессора TMS320C6201

Процессор TMS320C6201 состоит из трех основных частей: центрального процессора (ядро), периферийных устройств и памяти.

Ядром TMS320C6201 является VelociTI VLIW-процессор с 8 функциональными модулями, включая 2 умножителя и 6 АЛУ. Модули взаимодействуют через два регистровых файла, содержащих по 16 32-разрядных регистров. ЦП может выполнять до 8 команд за один такт.

Программный параллелизм выявляется на этапе компиляции, анализ зависимости по данным аппаратными средствами на стадии выполнения не производится. Код выполняется на независимых функциональных устройствах в последовательности, задаваемой программой.

В процессоре используется упаковка команд, сокращающая размеры кода и время выборки команд. 256-разрядная шина памяти программ позволяет выбирать за один такт восемь 32-разрядных команд. Все команды содержат условия их выполнения, что позволяет сократить расходы производительности процессора на выполнение переходов и увеличить степень параллелизма обработки.

Процессор может оперировать с 8/16/32-разрядными данными. Для приложений, требующих высокой точности вычислений, предусмотрена возможность вычислений с 40-разрядными операндами. Для результатов всех основных арифметических операций выполняется округление и нормализация. В процессоре реализованы операции над битовыми полями, такие как "выделить" (extract), "установить" (set), "очистить" (clear), "подсчет битов" (bit counting).

Центральный процессор имеет два тракта обработки данных, каждый из которых содержит функциональные модули (L, S, M, D) и регистровый файл (16 32-разрядных регистров). Функциональные модули выполняют сдвиг, умножение, логические и адресные операции. Все операции выполняются над регистрами. Два набора устройств адресации данных (D1 и D2) отвечают исключительно за все пересылки данных между регистровым файлом и памятью. Управляющий регистровый файл определяет различные аспекты функционирования процессора.

Процесс обработки VLIW начинается с выборки из памяти команд 256-битного пакета. Команды связываются для совместного выполнения в выполняемый пакет (до 8 команд) по значению младшего бита команды.

Устройство выборки-декодирования-диспетчеризации команд может направлять к функциональным модулям до 8 команд (32-разрядных) за один такт по каждому из путей обработки (А и В).

В С62хх реализованы прямой и циклический (для регистров А4-А7 и В4-В7) способы адресации. Способ адресации определяется регистром режима адресации (AMR - Address Mode Register).

Процессоры семейства С62хх имеют 14 прерываний, соответствующих сигналу Reset (Сброс), немаскируемому прерыванию (NMI - None Masked Interrupt) и прерываниям с номерами 4 -15.

С62хх содержат внутрикристальную память, которая может использоваться как память программ или кэш-память. Интерфейс внешней памяти процессора объединяет в единое адресное пространство внутреннюю и внешнюю память.

Внутрикристальная память разделена на память данных и память программ. Процессоры семейства С62хх имеют два 32-разрядных порта к памяти данных и один 256-разрядный порт к памяти программ для выборки инструкций. Процессор TMS320C6201 содержит на кристалле по 64 Кбайт памяти данных и программ. В процессоре используется расслоение памяти данных (четыре 16-разрядных банка) для повышения скорости выборки за счет одновременного обращения к различным банкам памяти.

Дополнительно процессоры семейства С62хх могут содержать на кристалле интерфейс внешней памяти, контроллер ПДП, интерфейс хост-порта (HPI), средства энергосбережения, расширенные буферизированные последовательные порты, 32-разрядные таймеры.

Следующий представитель семейства TMS320C6x - микропроцессор TMS320C6701 поддерживает операции с плавающей точкой, имеет более широкий (128 бит) интерфейс внешней памяти и меньшую частоту работы - 167 МГц.

В состав микропроцессора TMS320C6701 включены дополнительные функциональные модули:

Пиковая производительность данного микропроцессора составляет 688 Mflops.